Figure 1 from Dual-Gate Charge Trap Flash Memory for Highly Reliable Triple Level Cell Using Capacitive Coupling Effects | Semantic Scholar

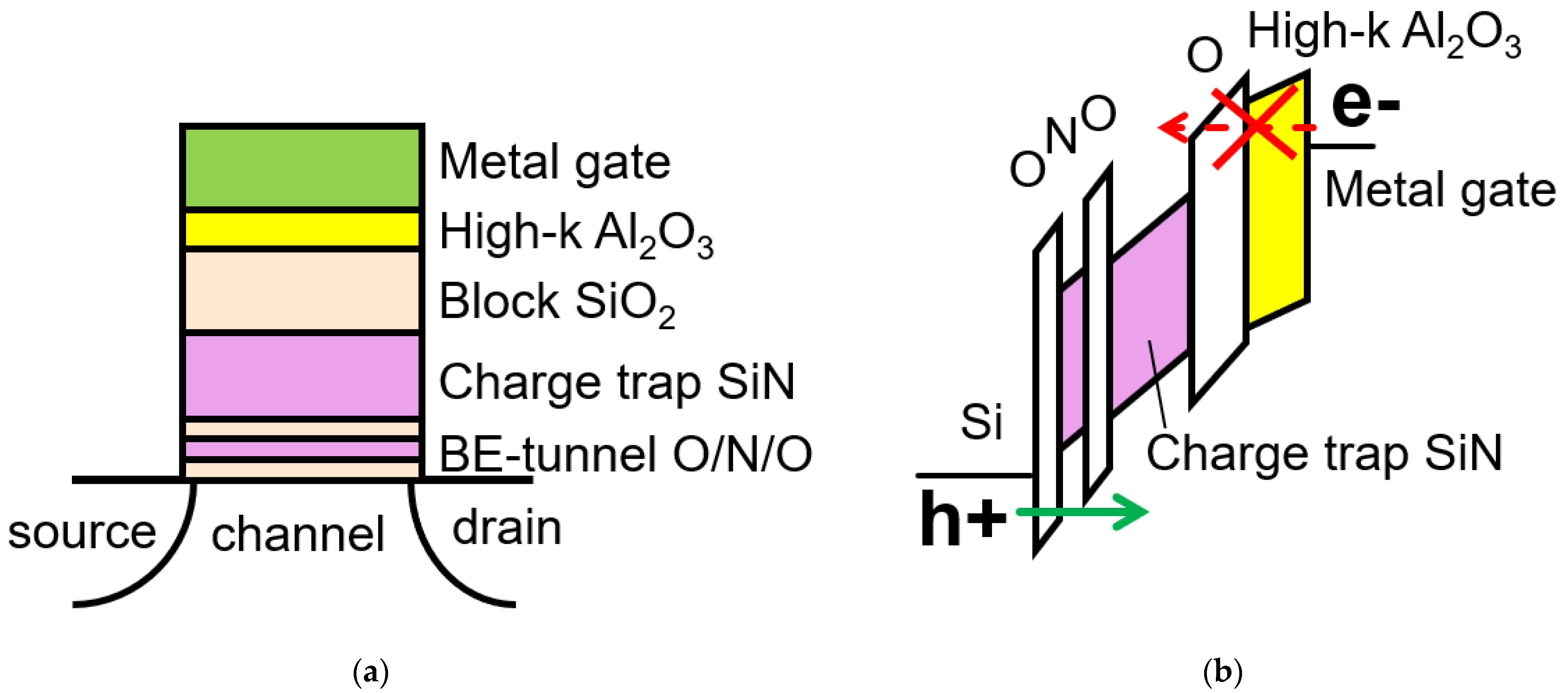

Figure 4 from Nonvolatile Poly-Si TFT Charge-Trap Flash Memory With Engineered Tunnel Barrier | Semantic Scholar

Investigating the Reasons for the Difficult Erase Operation of a Charge‐Trap Flash Memory Device with Amorphous Oxide Semiconductor Thin‐Film Channel Layers - Kim - 2021 - physica status solidi (RRL) – Rapid

_en.png)